ji��ֵ��������������ŷ(m��)�����£���zui����Ӧ�ÿ����ǵ������Ƶ�·�����ǵĵ�ֵ�ɽ�������ġ�������ЩӦ�ã���Լ10%-20%���ݲ���㹻�ˡ�����ʹ����Щ�ݲ��£�jingȷ�����dz��͵ĵ���ֵҲ�൱���ѣ����������漰�����ʱ��

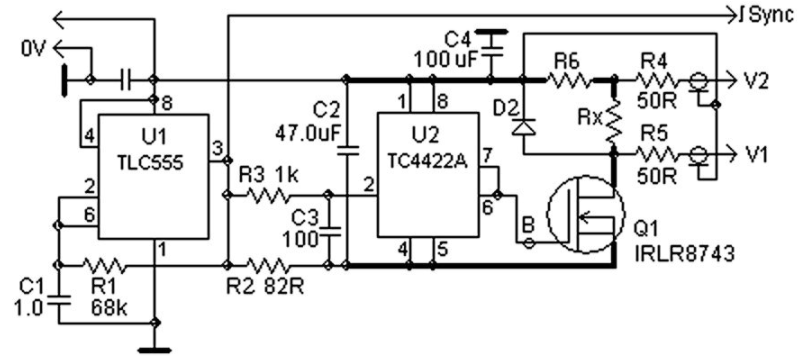

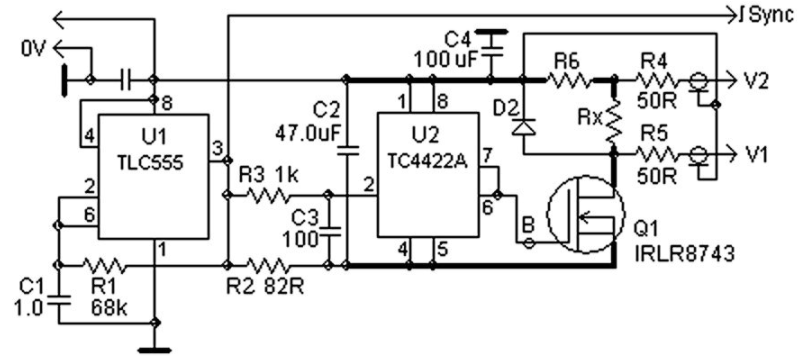

ͼ1����ʾ�ĵ�·ͨ����δ֪����������ֵ֪�IJο�������ʩ�ӵ�ռ�ձ����壬Ϊ�������ṩ�˽�����������ʼ������ڱȽ������������Ӧ��ȷ����������ֵ��

ͼ1��ʾ��·ͨ����δ֪����������ֵ֪�IJο�������ʩ�ӵ�ռ�ձ����壬����jingȷ����ji�͵ĵ���ֵ��

����jingȷ����ֵ����IJ���ֵ����ʹ����ͨʾ�����������ֵ��ѹ�������V1��v2��ã��������ṩ���ߵľ��ȡ�

�������ص�����ù��̽羪̾����������ύָ��

�õ�·ʹ�ù��ϵ�555��ʱ�����ڷ���̬ģʽ�������Բ������ڶԵ͵�е�����C2���ͷŵ�����塣�ڷŵ������У�����ͨ�����ܱ�����(R6)�ͱ������(Rx)��

����ֵ������Ӧ��ѹ�ı�ֵ����ó���

V1/V2=(Rx+R6)/R6=Rx/R6+1��

����V1��V2�Ƿ�ֵ��

��ˣ�δֵ֪��

Rx=(V1/V2�C1)*R6

ʾ����/��ѹ���Ĵ���Ӧ���㹻���Բ���·�����Ķ����塣����555�����İ��������������ʱ��ı��ʷdz���һЩʾ������ȷ���㹻�����ȡ�

�õ�·������������������Ҫ��������ͳ���ʱ���������ĵ͵��踺�أ�����뵼�弤������

���Ե�·ϸ��

����ͬ����U1������3��������ʾ����������ͬ����ͬ�����������֮����ӳٿ��ܻ�ʹʾ�������������ǰ�أ���ΪijЩʾ������Yͨ���п���û���ӳ��ߣ��Ӷ�����ʾ�dz����͵�ǰ�ء����ӳ���ʱ�䳣��R3*C3������C3��ֵ������20�C500pF���������ࣩ�ķ�Χ�ڣ�����ȡ������ʹ�õ�ʱ����ʾ����������

MOSFET������U2(TC4422A)����ȷ��Q1�ĸ�դji�������Ϳ��ٵ�ͨʱ�䣬�����jingȷ����������Ҫ��

MOSFET(Q1)���зdz��͵�RDSOn(����3��)����ȷ���ɾ��ĸ�������塣���ٶ�ji��D2����Q1�Ĺ�ѹ��ע�⣺�ⲿ�ֵ�·�г��ֵĸߵ�����Ҫ�ر�ע��Ԫ��ѡ���PCB���֡��й���ϸ��Ϣ���������������ѡ��˵�������˵�����֡�

�õ�·�Ķ̶�ǿ��ĵ������廹��Ƶ���в����˹�����Ӧ����ˣ������ر�ע�⾡�����ټ�����к͵��ݸ��أ������·����ʾ��ˮƽ�ĵ翹�����ڲ��ֵĸ������ֲ���������Ҫ�˽���й���ν���Щ����Ҫ�ļ���ЧӦ����zui�͵�ʵ��ϸ�ڼ�¼�ڱ��ĵ����˵�����֡�

Ԫ����ѡ��ע������

ǿ���Ƽ����ڵ�·��SMDԪ����һЩ����������ʹ�ǻ��ڱ�Ĥ�Ľṹ�����ܵ�����ĸߵ�������ʱ�����ǵĽ���Ҳ�ᾭ��ѹ���˶��������ڱ�¶��C2����Щ����ʱ���������ԴӴ���������������൱�����ġ��δ�����������ζ������ѹ��ЧӦ����ɵĸ�ˮƽ��ġ�����������£����δ𡱼���ϵ͵�������Ա���Ϊ���õ������

����TTElectronics��0.005��(5m��)��1%�ݲ�LOB-3���ܵ�������������(R6)��

���ڵ�·���ñ������������������Ԫ�����ݲ�Ǻܹؼ�����Ӧ�ر�ע�����ǵ��ȶ��Ժͽṹ������磬������C2��ֵ������Ҫ������Ӧ���㹻�����ṩ�㹻���ĵ������壬����ʾ�������ѹ��������ע���

�õ�����Ӧʹ�þ��е�����/��еĹ��켼����������㲭Ĥ���մɡ���Ӧ�ñ���ʹ�ö������͵ĵ��������������մɵ�������������ǵĵ���ȡ����ʩ�ӵĵ�ѹ�����б�Ҫ�����Բ�������������Բ��������ֵ��

����MOSFET������ji��RDSon������ʾ��������ti��CSD16321Q5������IR��IRLx8743�����ǣ���������ͨ��������Խϵ͵�©Դ��դԴ������ѹ��CSD16321Q5��Ϊ8V�����������������κ���ʱ��Ӧ���ǵ�DZ�����㡣

��һ��DZ��������MOSFET��zui��©ji��������������������Ӱ����Ե�·�IJ������ޡ�

Ϊ�˽��ͼ�����ˮƽ��������R6�͵�����C4Ӧ�þ��зdz��͵ĵ�С�����������Լ����������ӵ�PCB���ߡ�

��Ʊʼ�

R6��C4��Χ��PCB���߱��뱣�ֽ϶̺Ͳ��֣���zui���ȵؼ��ټ����翹�������翹�ᵼ�µ������弤���ľֲ�г�������·���ֲ����ϴ�Ҫ��������׳���MOSFETQ1��jue��zui����ѹ�����磬����6nF��դji���ݣ������Ը��أ�������TC4422A���������/�½�ʱ�����С��25ns����һ��ʵ����ͨ����еĴ����(~100A)��������������κ�MOSFET�ĵ�ѹ��

�����ԭ��ͼ�Բ鿴�Դ���ͻ����ʾ�����ߡ�����Щ���߱����㹻���Գ��ظߵ����������ܶ���zuiС��������С�����ڽ�դji���ӵ���������U2������6��Q1�Ļ�ji��������������Ҫ��������Ӧ������С��1Ӣ�硣�˼���(B)�ϵ�������������������Ʋ���Ҫ����

����ͬ����ԭ����Rx��R6������Ӧ�����ܽӽ���ͬ�ij��ȡ����ǻ�Ӧ�����̣ܶ���zui���ȵؼ��ٵ�к͵�ѹ����

��·�������ⲿ���Ӷ�Ӧʹ�û����ĸ�Ƶʵ��������ơ����磬����ʹ�����˾��������迹ƥ���50��ͬ����¡�